Introduction

Fault current calculations in most engineering textbooks start with a clean, symmetrical sine wave. Real fault currents do not. The moment a fault occurs in a power system, the current waveform is almost never symmetrical — and that asymmetry carries a hidden energy component that can push a current transformer core into saturation within the first half-cycle, long before any protection relay has had time to respond.

The direct answer: DC offset in fault current is a decaying unidirectional component superimposed on the symmetrical AC fault current, caused by the system’s inability to instantaneously change the inductive circuit’s current from its pre-fault value to the new steady-state fault level — and it is this transient component that dramatically amplifies peak flux demand on CT cores, often by a factor of 2× to 10× above the symmetrical fault value alone.

I’ve worked with protection engineers across industrial substations in Europe, the Middle East, and Southeast Asia, and the same blind spot appears repeatedly: fault level studies calculate symmetrical short-circuit current accurately, but the DC offset multiplier gets applied as a checkbox rather than a calculated engineering input. The result is CT specifications that look correct on paper but fail in the field during the first real asymmetrical fault. This article gives you the complete physics, the practical calculations, and the CT selection framework to close that gap. 🔍

Table of Contents

- What Is DC Offset in Fault Current and Where Does It Come From?

- How Does DC Offset Multiply Peak Flux Demand on CT Cores?

- How Do You Calculate DC Offset Severity and Select CTs Accordingly?

- What Installation and Maintenance Practices Reduce DC Offset Saturation Risk?

- FAQs About DC Offset in Fault Current

What Is DC Offset in Fault Current and Where Does It Come From?

To understand DC offset, you need to start with a fundamental property of inductive circuits1: current through an inductance cannot change instantaneously. This single physical constraint is the origin of every asymmetrical fault2 transient in a power system, and understanding it completely changes how you think about CT specification. ⚙️

The Physics of Fault Inception

When a fault occurs, the circuit transitions from its pre-fault state to a new steady-state fault condition. In a purely inductive system, the steady-state fault current is a symmetrical AC sine wave. However, the actual current at the instant of fault inception must equal the pre-fault current — it cannot jump discontinuously.

The total fault current is therefore the sum of two components:

Where:

- = symmetrical AC fault current component =

- = decaying DC offset component =

And:

- = voltage phase angle at fault inception

- = system impedance angle

- = DC time constant =

The Role of Fault Inception Angle

The magnitude of the DC offset is entirely determined by the voltage phase angle at the instant of fault inception:

| Fault Inception Angle | DC Offset Magnitude | Asymmetry Condition |

|---|---|---|

| 90° | Zero | Fully symmetrical fault — no DC offset |

| 45° | Partial asymmetry | |

| 0° | (maximum) | Fully asymmetrical fault — worst case |

The worst-case scenario — maximum DC offset — occurs when the fault initiates at the voltage zero crossing in a highly inductive system (where ). This is not a rare edge case. In high-voltage transmission systems with X/R ratios3 of 20 or higher, the impedance angle $\theta$ approaches 90°, and the probability of near-maximum DC offset is significant.

The DC Time Constant and Decay Rate

The DC component does not persist indefinitely — it decays exponentially with time constant . In practical power system terms:

- Distribution systems (X/R = 5–10): ms DC offset decays within 3–5 cycles

- Subtransmission systems (X/R = 10–20): ms DC offset persists for 5–10 cycles

- Transmission systems (X/R = 20–50): ms DC offset can persist for 10–25 cycles

This decay timeline is critical: high-speed protection must operate within the first 1–3 cycles — precisely when the DC offset is at or near its maximum value and CT saturation risk is highest.

Key Parameters Governing DC Offset Severity

| Parameter | Symbol | Effect on DC Offset | Typical Range |

|---|---|---|---|

| X/R Ratio | Higher larger slower decay | 5 – 50 | |

| DC Time Constant | (ms) | Longer DC persists longer | 16 – 160ms |

| Fault Inception Angle | Closer to 0° larger initial DC | 0° – 90° | |

| Symmetrical Fault Current | Higher larger absolute DC magnitude | System dependent |

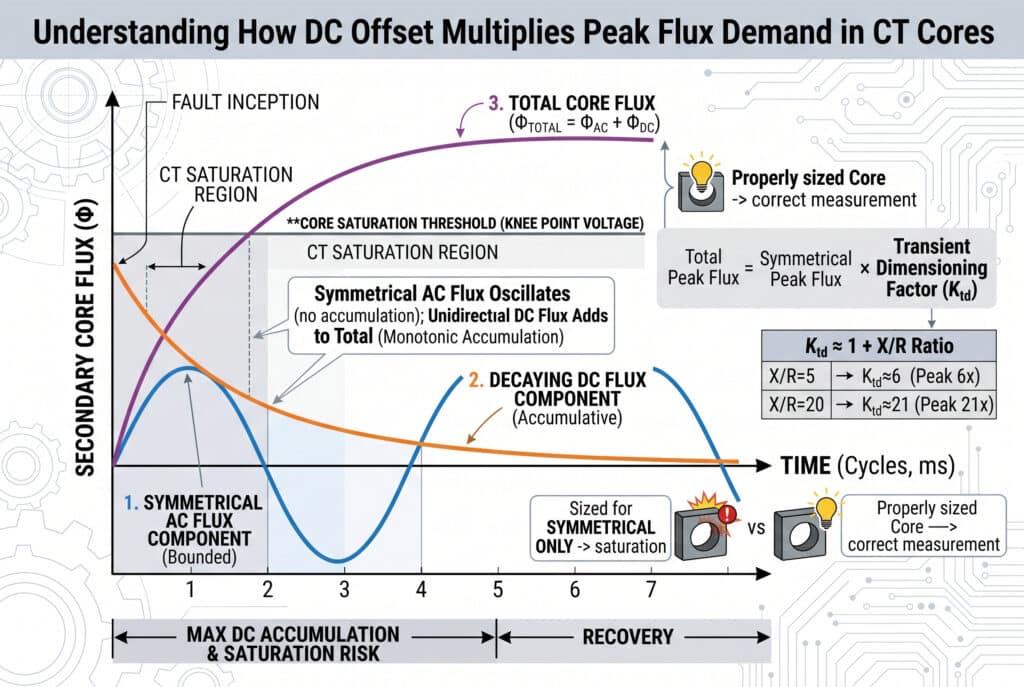

How Does DC Offset Multiply Peak Flux Demand on CT Cores?

This is the section that most CT specification guides skip over — the direct, quantitative link between DC offset in the primary fault current and flux accumulation in the CT core. Understanding this mechanism is what separates engineers who specify CTs correctly from those who discover the problem after a protection failure. 🔬

From Primary Current to Core Flux

The CT core flux is the time integral of the applied secondary voltage, which is proportional to the primary current. For the symmetrical AC component alone, the flux oscillates symmetrically around zero — the positive and negative half-cycles cancel, and the peak flux remains bounded.

The DC offset component behaves fundamentally differently. Because it is unidirectional, its flux contribution accumulates monotonically — it adds to the core flux in one direction without cancellation. The total core flux at any instant is:

Where grows from zero at fault inception, reaches a peak, then decays as the DC component itself decays. The peak total flux demand occurs not at , but at approximately (one time constant after fault inception) — which can be 32–160ms into the fault event.

The Transient Dimensioning Factor4 ()

IEC 61869-2 quantifies the total flux demand multiplier through the Transient Dimensioning Factor:

For practical engineering, the simplified conservative expression is widely used:

This means:

| System X/R Ratio | (Approximate) | Peak Flux vs. Symmetrical Only |

|---|---|---|

| X/R = 5 | ~6 | 6× symmetrical flux demand |

| X/R = 10 | ~11 | 11× symmetrical flux demand |

| X/R = 20 | ~21 | 21× symmetrical flux demand |

| X/R = 30 | ~31 | 31× symmetrical flux demand |

The engineering implication is stark: a CT correctly sized for symmetrical fault current at an X/R = 20 bus needs a knee point voltage 21 times higher than the symmetrical burden voltage alone. Ignoring this multiplier is not a conservative approximation — it is a fundamental specification error.

Flux Accumulation Timeline

The CT core saturation5 follows a predictable pattern that protection engineers must internalize:

- Cycle 1 (0–20ms): DC offset near maximum flux accumulates rapidly saturation most likely

- Cycles 2–3 (20–60ms): DC decaying flux accumulation slowing partial saturation possible

- Cycles 4+ (>60ms): DC substantially decayed flux returns toward symmetrical behavior CT recovers

Customer Story: A protection engineer named Thomas, working on a 66kV grid connection project for an industrial park in Bavaria, Germany, specified Class P CTs with ALF 20 based on the symmetrical fault level of 16kA. The system X/R ratio at that bus was 25. During commissioning, a staged fault test revealed that the CTs saturated within the first cycle — the distance relay’s Zone 1 failed to operate. Recalculating with showed the required knee point voltage was 4.3× higher than specified. Bepto supplied replacement Class TPY CTs with the correct transient dimensioning, and the protection scheme passed all staged fault tests on the first retest. ✅

Impact on Different CT Core Types

Not all cores respond to DC flux accumulation equally:

- Standard silicon steel (GOES) cores: High remanence ( 60–80%) means residual flux from previous events adds directly to DC-driven flux accumulation — worst-case saturation risk

- Nickel-iron alloy cores: Sharp knee point and moderate remanence — predictable saturation boundary but still vulnerable at high X/R ratios without proper sizing

- Nanocrystalline cores (Class TPZ): Near-zero remanence () and air-gap design — dramatically reduced DC flux accumulation, best transient performance

How Do You Calculate DC Offset Severity and Select CTs Accordingly?

Correct CT selection for DC offset conditions is a calculation-driven process. There is no conservative rule of thumb that substitutes for the actual numbers. Here is the complete step-by-step framework. 📐

Step 1: Determine System X/R Ratio at the Fault Point

Obtain the X/R ratio from your network fault study at the specific bus where the CT will be installed. Do not use a generic system-wide value — X/R varies significantly with location in the network:

- Generator terminals: X/R = 30–80 (highest DC offset risk)

- HV transmission buses: X/R = 20–40

- MV distribution substations: X/R = 10–20

- LV industrial systems: X/R = 5–10

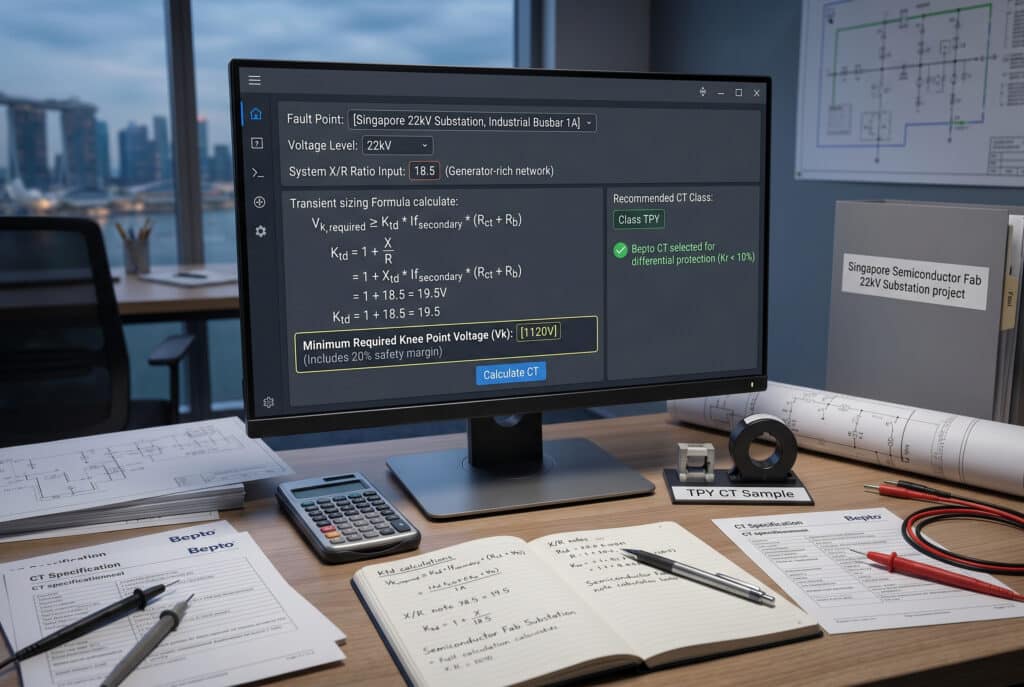

Step 2: Calculate the Required Knee Point Voltage

Apply the full transient sizing formula per IEC 61869-2:

Where:

- — transient dimensioning factor

- = maximum symmetrical fault current in secondary amperes

- = CT secondary winding resistance

- = total connected burden resistance

Apply a minimum 20% safety margin above the calculated value to account for:

- Measurement uncertainty in X/R ratio

- Residual flux from previous fault events

- Burden calculation tolerances

Step 3: Select the Appropriate CT Accuracy Class

| Protection Application | DC Offset Severity | Recommended CT Class | Remanence Requirement |

|---|---|---|---|

| Overcurrent relay (50/51) | Low–Medium (X/R <10) | Class P, ALF 20–30 | Not specified |

| Overcurrent relay (50/51) | High (X/R >10) | Class PX with calculated | Not specified |

| Differential relay (87T/87B) | Any | Class TPY or TPZ | |

| Distance relay (21) | Medium–High | Class TPY | |

| Auto-reclose scheme | Any | Class PR or TPY | |

| Busbar protection (87B) | High | Class TPZ (air-gap) | Near zero |

Step 4: Verify Environmental and Installation Conditions

- Indoor MV switchgear (≤40°C): Standard thermal class B acceptable

- Outdoor installations or tropical climates (>40°C): Thermal Class F or H required

- Coastal or chemical environments: IP65 enclosure, corrosion-resistant terminal materials

- High-altitude installations (>1000m): Apply IEC derating factors for dielectric and thermal performance

Step 5: Confirm Through Factory and Site Testing

Before energization, verify DC offset performance capability through:

- Factory Acceptance Test (FAT): Review magnetization curve certificate — confirm measured $V_k$ matches specification

- Secondary injection test on-site: Plot V-I excitation curve and verify knee point location

- Burden measurement: Measure actual installed burden with a precision impedance meter — do not rely on calculated estimates

- Remanence check: For Class TPY/TPZ CTs, verify remanence specification on the test certificate

Customer Story: Sarah, a procurement manager at an EPC contractor in Singapore handling a 22kV industrial substation for a semiconductor fab, initially received CT quotations from three suppliers — all claiming Class TPY compliance. When she requested factory magnetization test certificates, only Bepto’s documentation included measured Ktd verification data alongside the standard V-I curve. The other two suppliers could not produce equivalent documentation. Her client’s protection engineer accepted only the Bepto CTs for the project, citing the completeness of the technical evidence package. 💡

What Installation and Maintenance Practices Reduce DC Offset Saturation Risk?

Even a correctly specified CT can have its DC offset performance compromised by poor installation practices or inadequate post-fault maintenance. These are the field-level disciplines that protect your protection system’s integrity over its operational lifetime.

Installation Checklist

- Minimize secondary cable length — every additional meter of cable adds resistance to the burden, directly reducing the effective safety margin above the required knee point voltage

- Verify polarity before energization — reversed P1/P2 or S1/S2 connections cause differential relay maloperation that mimics saturation-induced false differential current

- Measure and document actual burden — use a precision impedance bridge to measure total secondary circuit resistance including all relay inputs, test switches, and terminal contact resistances

- Perform demagnetization before commissioning — apply AC demagnetization to eliminate any residual flux from factory testing or transport magnetization

- Record baseline magnetization curve — retain the site-measured V-I curve as a reference for all future maintenance comparisons

Common Mistakes That Worsen DC Offset Saturation

- Applying symmetrical fault current without Ktd multiplier — the most common and most consequential CT sizing error in MV/HV protection engineering

- Ignoring residual flux accumulation in auto-reclose schemes — each successive reclose attempt adds residual flux if the core does not fully demagnetize between events; Class PR or TPY cores are mandatory for these applications

- Mixing CT classes within a differential protection zone — pairing a Class PX CT on one terminal with a Class P CT on another creates unequal saturation behavior under DC offset conditions, generating false differential current

- Failing to re-verify burden after panel modifications — adding relay inputs, test plugs, or monitoring equipment after initial commissioning increases burden and reduces DC offset performance margin without any visible indication

- Skipping post-fault demagnetization — after any close-in fault with significant DC offset, the core retains residual flux that can occupy 40–80% of available headroom; the next fault event starts with a severely compromised CT

Recommended Maintenance Intervals

| Activity | Trigger | Interval |

|---|---|---|

| Magnetization curve verification | Commissioning + periodic | Every 5 years |

| Burden measurement | After any panel modification | As required |

| Core demagnetization | After close-in fault event | Post-fault |

| Visual and terminal inspection | Scheduled maintenance | Annual |

| Full secondary injection test | Major substation outage | Every 10 years |

Conclusion

DC offset in fault current is not a secondary consideration in CT specification — it is the primary driver of peak flux demand during the most critical window of protection system operation. The transient dimensioning factor transforms a routine CT sizing exercise into a calculation that can mean the difference between a relay that trips in 20 milliseconds and one that fails entirely. Specify your CTs with the full transient flux demand in mind, verify with measured magnetization curves, and maintain your cores with the discipline that high-speed protection demands. Get the DC offset calculation right, and your protection system will perform when it matters most. 🔒

FAQs About DC Offset in Fault Current

Q: What is the maximum possible DC offset in a fault current and under what system conditions does it occur?

A: Maximum DC offset equals the peak symmetrical fault current magnitude, occurring when fault inception angle equals zero in a purely inductive system. In practice, transmission systems with X/R ratios above 30 approach this worst-case condition, making transient CT sizing essential for all HV protection schemes.

Q: Why does a higher X/R ratio increase CT saturation risk during asymmetrical faults?

A: Higher X/R ratio means a longer DC time constant , so the DC offset decays more slowly. The core flux accumulates over more cycles before the DC component dissipates, increasing both the peak flux demand and the duration of potential saturation — directly multiplying the required CT knee point voltage.

Q: How does residual remanent flux interact with DC offset to worsen CT saturation?

A: Remanent flux from previous fault events or switching operations pre-occupies core capacity before the new fault begins. When DC offset then drives additional unidirectional flux accumulation, the core reaches saturation at a lower primary current level — effectively reducing the CT’s functional knee point voltage below its rated value.

Q: Is DC offset present in three-phase faults or only in single-phase faults?

A: DC offset occurs in all fault types — three-phase, phase-to-phase, and single-phase — whenever the fault inception angle produces a non-zero initial condition. In three-phase faults, the DC offset magnitude differs across the three phases depending on each phase’s voltage angle at fault inception, with at least one phase experiencing significant asymmetry.

Q: What is the difference between Class TPY and Class TPZ CTs in handling DC offset transients?

A: Class TPY specifies defined transient performance with remanence limited to <math data-latex="K_r

-

Understand the fundamental physical principles governing current behavior in inductive power circuits. ↩

-

Explore the mathematical breakdown of AC and DC components during power system short circuits. ↩

-

Learn how to determine X/R ratios and their critical role in transient stability and relay coordination. ↩

-

Deep dive into the international standard for dimensioning CTs for transient performance. ↩

-

Review the technical mechanics of magnetic flux accumulation and its effect on CT accuracy. ↩